# Übung zu Betriebssysteme

Zeitscheibenscheduling

09. Januar 2024

Maximilian Ott, Dustin Nguyen, Phillip Raffeck & Bernhard Heinloth

Lehrstuhl für Informatik 4 Friedrich-Alexander-Universität Erlangen-Nürnberg

# Motivation

# Kooperative Ablaufplanung

```

int i = 0;

while (true){

Guarded section;

kout << i++ << endl;

scheduler.resume();

}</pre>

```

# **Unterbrechende Ablaufplanung**

```

int i = 0;

while (true){

Guarded section;

kout << i++ << endl;

}</pre>

```

# **Unterbrechende Ablaufplanung**

# Unterbrechende Ablaufplanung

Aufgabe: Präemptives Scheduling mittels Timer.

# Zeitgeber

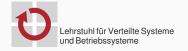

- Standardtimer seit 1981 (IBM-PC, Intel 8253/8254)

- ca. 1 193 182 Hz (=  $\frac{1}{3}$  NTSC-Freq.)

- → Genauigkeit: 838 ns

- drei Kanäle mit je einen 16 bit Zähler

- Kanal o löst standardmäßig alle 54.9254ms IRQ o aus

- Kanal 1 früher für Arbeitsspeicher

- Kanal 2 für PC Speaker (Tonfrequenz)

```

■ Standardtimer seit 1981 (IBM-PC, Intel 8253/8254)

a ca. 1 193 182 Hz (= \frac{1}{2} NTSC-Freq.)

→ Genauig PIC 8259A

CPU

■ drei Kanäle m t je einen 16 bit Zähler

Kanal o löst standardmäßig alle 54.9254ms IRQ o aus

Kanal 1 früher für Arbeitsspeicher

Kanal 2 für PC Speaker (Tonfrequenz)

PIT

Timer 1

Arbeitsspeicher

Timer 2

Systemlautsprecher

Timer 3

```

- Standardtimer seit 1981 (IBM-PC, Intel 8253/8254)

- ca. 1 193 182 Hz (=  $\frac{1}{3}$  NTSC-Freq.)

- → Genauigkeit: 838 ns

- drei Kanäle mit je einen 16 bit Zähler

Kanal o löst standardmäßig alle 54.9254ms IRQ o aus

Kanal 1 früher für Arbeitsspeicher

Kanal 2 für PC Speaker (Tonfrequenz)

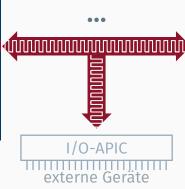

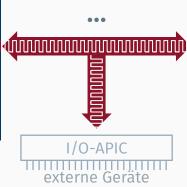

via PIC bzw. I/O APIC → (relativ) langsam

- Standardtimer seit 1981 (IBM-PC, Intel 8253/8254)

- ca. 1 193 182 Hz (=  $\frac{1}{3}$  NTSC-Freq.)

- → Genauigkeit: 838 ns

- drei Kanäle mit je einen 16 bit Zähler

Kanal o löst standardmäßig alle 54.9254ms IRQ o aus

Kanal 1 früher für Arbeitsspeicher

Kanal 2 für PC Speaker (Tonfrequenz)

- via PIC bzw. I/O APIC → (relativ) langsam

- ausreichend für BS

- Standardtimer seit 1981 (IBM-PC, Intel 8253/8254)

- ca. 1 193 182 Hz (=  $\frac{1}{3}$  NTSC-Freq.)

- → Genauigkeit: 838 ns

- drei Kanäle mit je einen 16 bit Zähler

Kanal o löst standardmäßig alle 54.9254ms IRQ o aus

Kanal 1 früher für Arbeitsspeicher

Kanal 2 für PC Speaker (Tonfrequenz)

- via PIC bzw. I/O APIC → (relativ) langsam

- ausreichend für BS (bis WS13), geht aber besser.

- → machine/pit.h

### Real Time Clock (RTC)

- seit 1984 (IBM-PC/AT)

- 32 768 Hz (= 2<sup>15</sup> Hz, Verwendung in Uhren)

- Standardmäßig Interrupts bei 1 024 Hz (fast 1 ms)

- 12 weitere Möglichkeiten von 2 bis 8 192 Hz durch Vorteiler

- IRQ 8 (Problem?)

- für Zeit & Datum

- Betrieb im ausgeschalteten Zustand mittels Batterie

- seit 1993 (Pentium)

- 64 bit, auslesbar über Assemblerinstruktion rdtsc

- Taktfrequenz wie CPU

- seit 1993 (Pentium)

- 64 bit, auslesbar über Assemblerinstruktion rdtsc

- Taktfrequenz wie CPU

- ursprünglich Erhöhung mit jedem Clock-Signal

- unterschiedliche Takte abhängig vom Stromsparmodus

- bei neueren Versionen: konstante Rate entsprechend nominaler Geschwindigkeit

- seit 1993 (Pentium)

- 64 bit, auslesbar über Assemblerinstruktion rdtsc

- Taktfrequenz wie CPU

- ursprünglich Erhöhung mit jedem Clock-Signal

- unterschiedliche Takte abhängig vom Stromsparmodus

- bei neueren Versionen: konstante Rate entsprechend nominaler Geschwindigkeit

- kann keinen Interrupt auslösen

- seit 1993 (Pentium)

- 64 bit, auslesbar über Assemblerinstruktion rdtsc

- Taktfrequenz wie CPU

- ursprünglich Erhöhung mit jedem Clock-Signal

- unterschiedliche Takte abhängig vom Stromsparmodus

- bei neueren Versionen: konstante Rate entsprechend nominaler Geschwindigkeit

- kann keinen Interrupt auslösen

- → machine/tsc.h

# **ACPI Power Management Timer**

- seit es ACPI-Mainboards gibt (1996)

- 3 579 545 Hz (= NTSC-Freq.)

- ein 24 oder 32 bit Zähler

- besser als alte (nicht konstante) TSC

- Zugriff über I/O Port

- kann auch keinen Interrupt auslösen

# High Precision Event Timer (HPET)

- von Intel und Microsoft 2005 als PIT- & RTC-Ersatz veröffentlicht

- > 10 MHz

- → Genauigkeit: 100 ns oder besser

- ein 64 bit Zähler

- min. drei 32 oder 64 bit breite Vergleichseinrichtungen

- konfigurierbarer Interrupt bei Gleichheit

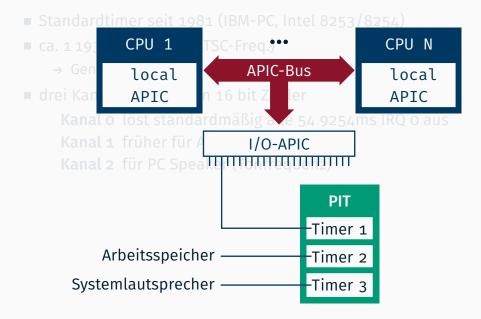

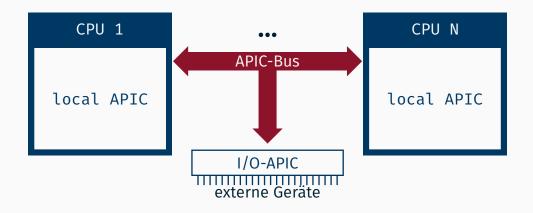

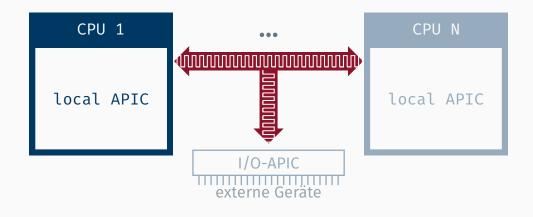

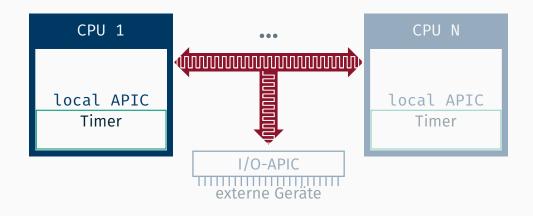

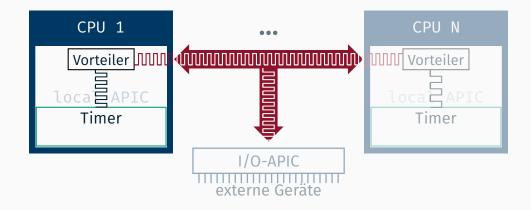

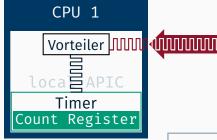

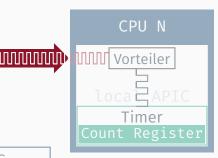

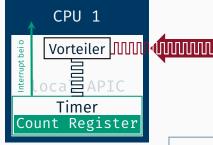

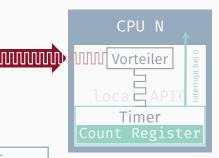

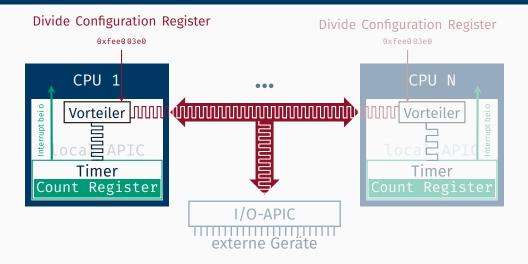

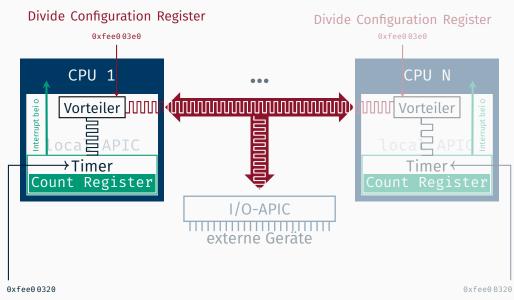

#### **LAPIC Timer**

- > 100 MHz

- → Genauigkeit: 10 ns oder besser

- 32 bit Zähler

- verwendet Busfrequenz

- abhängig vom System

- aber unabhängig von Stromsparmodus

- Interrupt geht nur an den entsprechenden Kern

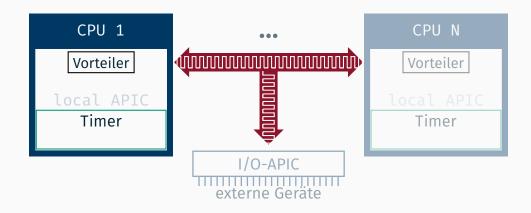

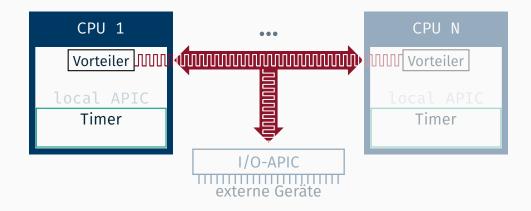

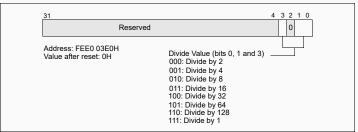

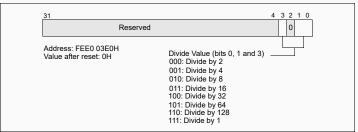

- 8 Möglichkeiten (bis  $\frac{1}{128}$  Busfrequenz) durch Vorteiler

#### **LAPIC Timer**

- > 100 MHz

- → Genauigkeit: 10 ns oder besser

- 32 bit Zähler

- verwendet Busfrequenz

- abhängig vom System

- aber unabhängig von Stromsparmodus

- Interrupt geht nur an den entsprechenden Kern

- 8 Möglichkeiten (bis  $\frac{1}{128}$  Busfrequenz) durch Vorteiler

#### Perfekt für unsere Bedürfnisse

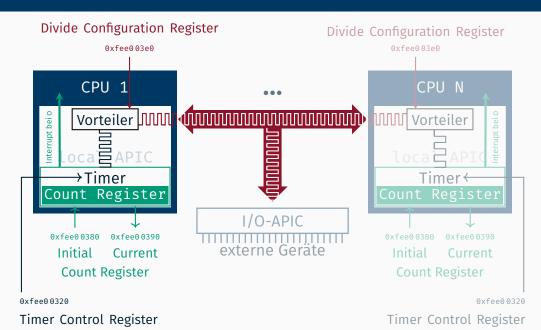

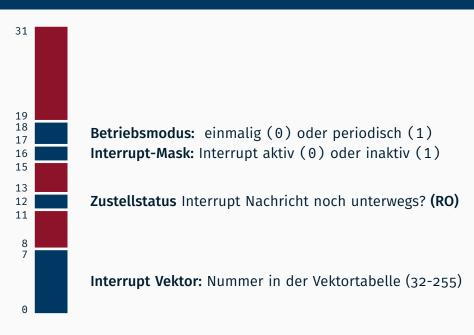

Timer Control Register

Timer Control Register

# Aufbau des Timer Control Register Eintrags

# **Zusammenfassung LAPIC Timer**

- jede CPU hat einen eigenen 32bit Timer

- Änderung am INITIAL COUNT REGISTER startet den Timer

- zu Beginn wird der initiale Startzählwert aus dem INITIAL COUNT REGISTER in das CURRENT COUNT REGISTER kopiert

- welches im Bustakt dekrementiert wird

- bei o wird sofern aktiviert ein Interrupt ausgelöst

- je nach Betriebsmodus wird gestoppt oder wieder neu begonnen

# Umsetzung

windup stellt das Unterbrechungsintervall ein (z.B. alle 1000 Mikrosekunden)

windup stellt das Unterbrechungsintervall ein (z.B. alle 1000 Mikrosekunden)

activate setzt den Timer und aktiviert Interrupts

windup stellt das Unterbrechungsintervall ein (z.B. alle 1000 Mikrosekunden)

activate setzt den Timer und aktiviert Interrupts

prologue fordert Epilog an

(und kann zu Testzwecken eine Ausgabe tätigen)

## Frequenz des LAPIC-Timers?

#### 10.5.4 APIC Timer

The local APIC unit contains a 32-bit programmable timer that is available to software to time events or operations. This timer is set up by programming four registers: the divide configuration register (see Figure 10-10), the initial-count and current-count registers (see Figure 10-11), and the LVT timer register (see Figure 10-8).

If CPUID.06H:EAX.ARAT[bit 2] = 1, the processor's APIC timer runs at a constant rate regardless of P-state transitions and it continues to run at the same rate in deep C-states.

If CPUID.06H:EAX.ARAT[bit 2] = 0 or if CPUID 06H is not supported, the APIC timer may temporarily stop while the processor is in deep C-states or during transitions caused by Enhanced Intel SpeedStep® Technology.

Figure 10-10. Divide Configuration Register

The APIC timer frequency will be the processor's bus clock or core crystal clock frequency (when TSC/core crystal clock ratio is enumerated in CPUID leaf 0x15) divided by the value specified in the divide configuration register.

## Frequenz des LAPIC-Timers?

#### 10.5.4 APIC Timer

The local APIC unit contains a 32-bit programmable timer that is available to software to time events or operations. This timer is set up by programming four registers: the divide configuration register (see Figure 10-10), the initial-count and current-count registers (see Figure 10-11), and the LVT timer register (see Figure 10-8).

If CPUID.06H:EAX.ARAT[bit 2] = 1, the processor's APIC timer runs at a constant rate regardless of P-state transitions and it continues to run at the same rate in deep C-states.

If CPUID.06H:EAX.ARAT[bit 2] = 0 or if CPUID 06H is not supported, the APIC timer may temporarily stop while the processor is in deep C-states or during transitions caused by Enhanced Intel SpeedStep® Technology.

Figure 10-10. Divide Configuration Register

The APIC timer frequency will be the processor's bus clock or core crystal clock frequency (when TSC/core crystal clock ratio is enumerated in CPUID leaf 0x15) divided by the value specified in the divide configuration register.

#### 1. LAPIC-Timer kalibrieren

unter Verwendung des PIT

(mittels PIT::set Wartezeit einstellen und in PIT::waitForTimeout warten)

- unter Verwendung des PIT (mittels PIT::set Wartezeit einstellen und in PIT::waitForTimeout warten)

- in der Funktion LAPIC::Timer::ticks(Funktion gibt die Anzahl der Ticks in einer Millisekunde zurück)

- unter Verwendung des PIT (mittels PIT::set Wartezeit einstellen und in PIT::waitForTimeout warten)

- in der Funktion LAPIC::Timer::ticks(Funktion gibt die Anzahl der Ticks in einer Millisekunde zurück)

- benötigt zur Konfiguration die ebenfalls noch zu implementierende Funktion LAPIC::Timer::set

- unter Verwendung des PIT (mittels PIT::set Wartezeit einstellen und in PIT::waitForTimeout warten)

- in der Funktion LAPIC::Timer::ticks(Funktion gibt die Anzahl der Ticks in einer Millisekunde zurück)

- benötigt zur Konfiguration die ebenfalls noch zu implementierende Funktion LAPIC::Timer::set

- Hilfsstrukturen in lapic\_timer.cc & lapic\_registers.h

#### 2. Initialen Wert und Vorteiler korrekt setzen

■ Interrupt soll alle *n* Mikrosekunden ausgelöst werden

- Interrupt soll alle *n* Mikrosekunden ausgelöst werden

- Startwertzähler  $initial = \frac{n \cdot LAPIC::Timer::ticks()}{Vorteiler \cdot 1000}$  berechnen, dabei gilt  $Vorteiler = 2^x \text{ mit } x \in \{0, \dots, 7\}$

- Interrupt soll alle *n* Mikrosekunden ausgelöst werden

- Startwertzähler  $initial = \frac{n \cdot LAPIC::Timer::ticks()}{Vorteiler \cdot 1000}$  berechnen, dabei gilt  $Vorteiler = 2^x \text{ mit } x \in \{0, ..., 7\}$

- Möglichst kleiner Vorteiler, aber kein Überlauf (32 bit!)

#### 2. Initialen Wert und Vorteiler korrekt setzen

- Interrupt soll alle *n* Mikrosekunden ausgelöst werden

- Startwertzähler  $initial = \frac{n \cdot LAPIC::Timer::ticks()}{Vorteiler \cdot 1000}$  berechnen, dabei gilt  $Vorteiler = 2^x \text{ mit } x \in \{0, \dots, 7\}$

- Möglichst kleiner Vorteiler, aber kein Überlauf (32 bit!)

- Beispiel: watch.windup(5000000);

```

n = 50000000 \, \mu s = 5 \, s

```

LAPIC::Timer::ticks 1000000 ms<sup>-1</sup>

- Interrupt soll alle *n* Mikrosekunden ausgelöst werden

- Startwertzähler  $initial = \frac{n \cdot LAPIC::Timer::ticks()}{Vorteiler \cdot 1000}$  berechnen, dabei gilt  $Vorteiler = 2^x \text{ mit } x \in \{0, ..., 7\}$

- Möglichst kleiner Vorteiler, aber kein Überlauf (32 bit!)

- Beispiel: watch.windup(5000000);

n 5000000 µs = 5 s

LAPIC::Timer::ticks 1000000 ms<sup>-1</sup>

Vorteiler 1 = 2°

- Interrupt soll alle *n* Mikrosekunden ausgelöst werden

- Startwertzähler  $initial = \frac{n \cdot LAPIC::Timer::ticks()}{Vorteiler \cdot 1000}$  berechnen, dabei gilt  $Vorteiler = 2^x \text{ mit } x \in \{0, ..., 7\}$

- Möglichst kleiner Vorteiler, aber kein Überlauf (32 bit!)

- Interrupt soll alle *n* Mikrosekunden ausgelöst werden

- Startwertzähler  $initial = \frac{n \cdot LAPIC::Timer::ticks()}{Vorteiler \cdot 1000}$  berechnen, dabei gilt  $Vorteiler = 2^x \text{ mit } x \in \{0, \dots, 7\}$

- Möglichst kleiner Vorteiler, aber kein Überlauf (32 bit!)

- Interrupt soll alle *n* Mikrosekunden ausgelöst werden

- Startwertzähler  $initial = \frac{n \cdot LAPIC::Timer::ticks()}{Vorteiler \cdot 1000}$  berechnen, dabei gilt  $Vorteiler = 2^x \text{ mit } x \in \{0, \dots, 7\}$

- Möglichst kleiner Vorteiler, aber kein Überlauf (32 bit!)

- Interrupt soll alle *n* Mikrosekunden ausgelöst werden

- Startwertzähler  $initial = \frac{n \cdot LAPIC::Timer::ticks()}{Vorteiler \cdot 1000}$  berechnen, dabei gilt  $Vorteiler = 2^x \text{ mit } x \in \{0, \dots, 7\}$

- Möglichst kleiner Vorteiler, aber kein Überlauf (32 bit!)

- Interrupt soll alle *n* Mikrosekunden ausgelöst werden

- Startwertzähler  $initial = \frac{n \cdot LAPIC::Timer::ticks()}{Vorteiler \cdot 1000}$  berechnen, dabei gilt  $Vorteiler = 2^x \text{ mit } x \in \{0, \dots, 7\}$

- Möglichst kleiner Vorteiler, aber kein Überlauf (32 bit!)

- Beispiel: watch.windup(5000000);

n 5000000 μs = 5 s

LAPIC::Timer::ticks 1000000 ms<sup>-1</sup>

Vorteiler 2 = 2<sup>1</sup>

initial 2500000000 √

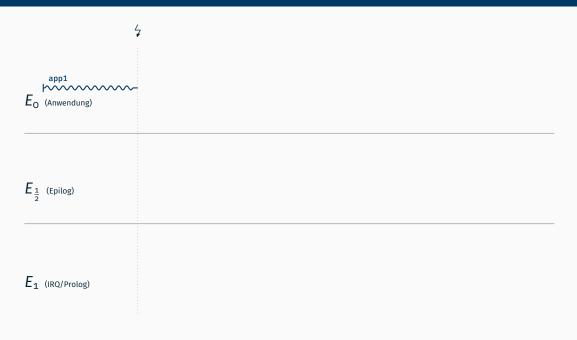

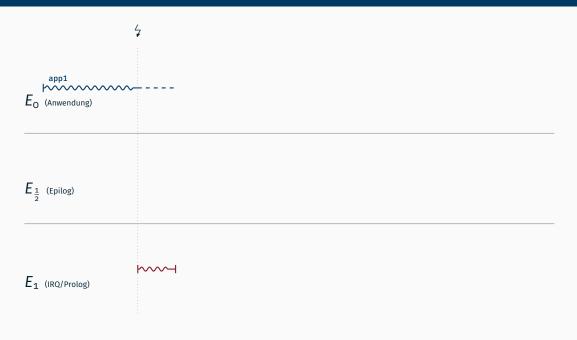

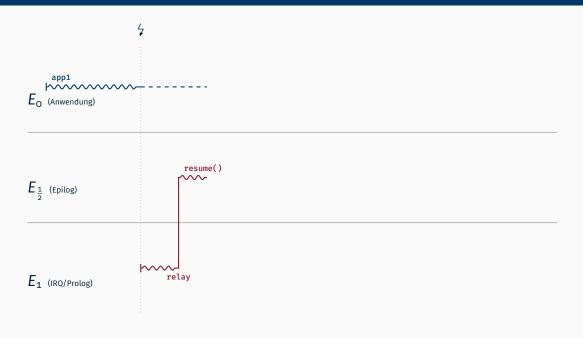

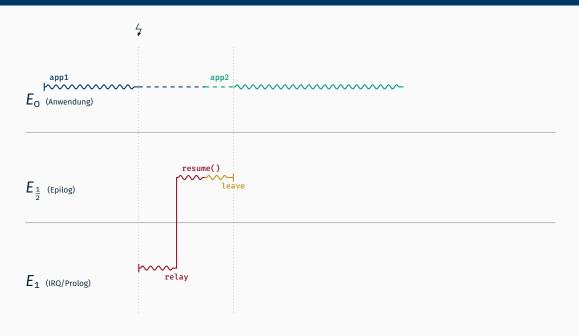

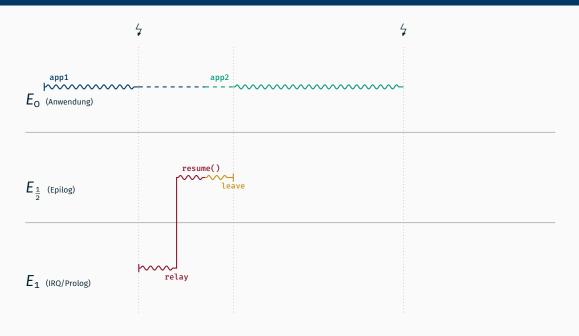

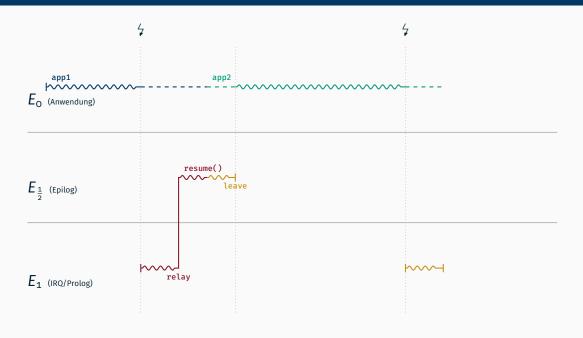

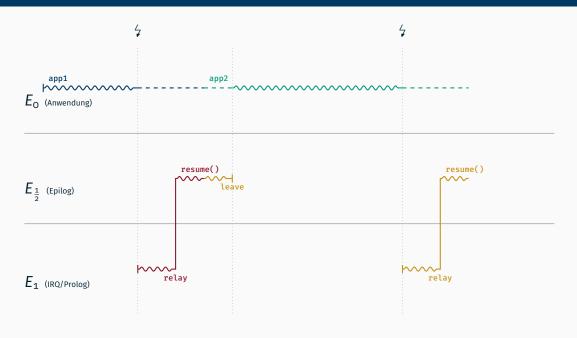

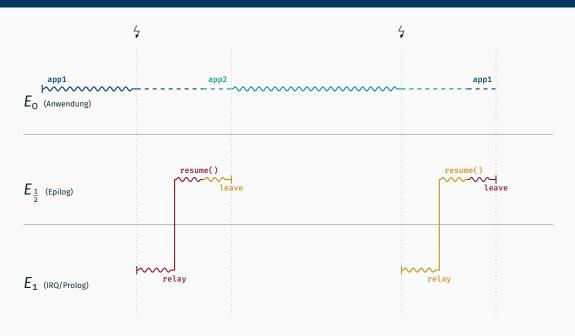

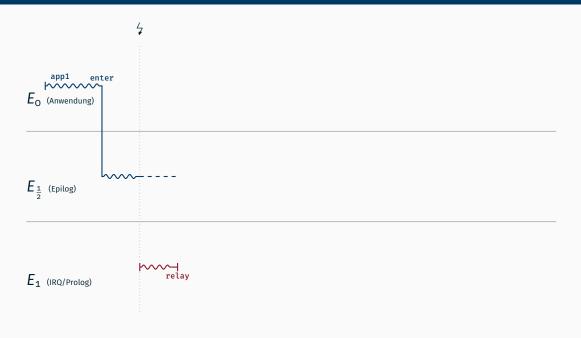

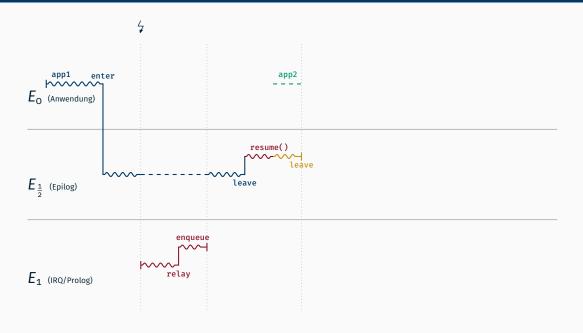

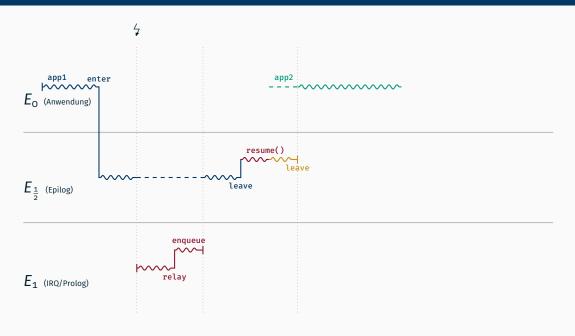

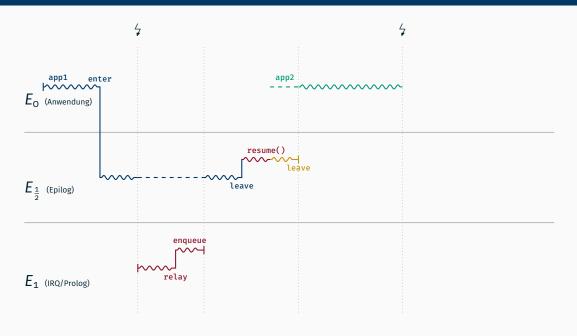

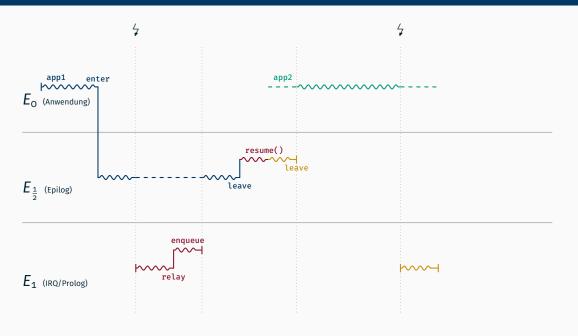

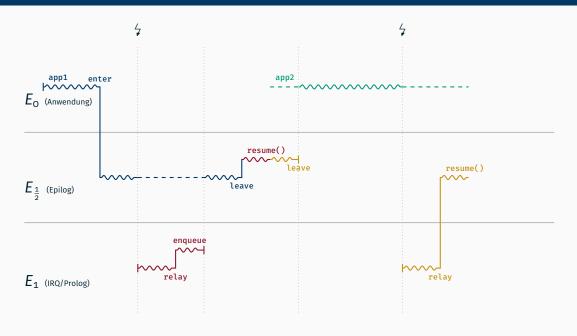

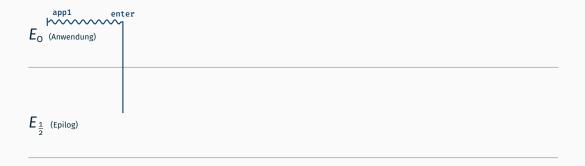

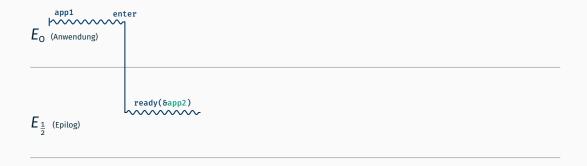

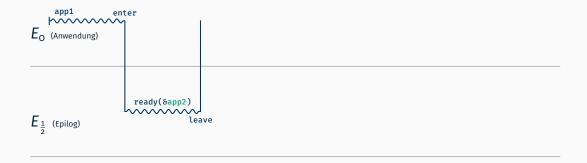

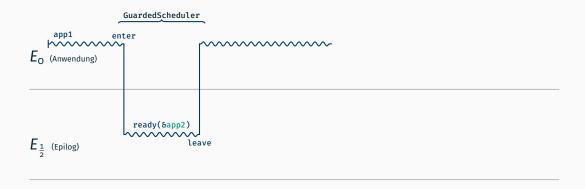

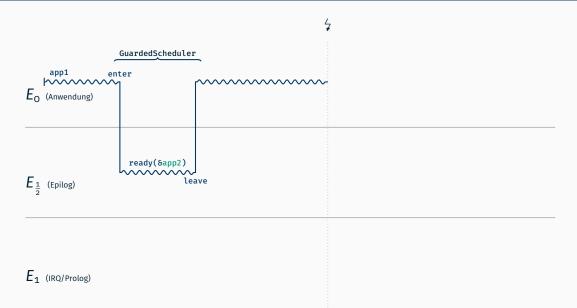

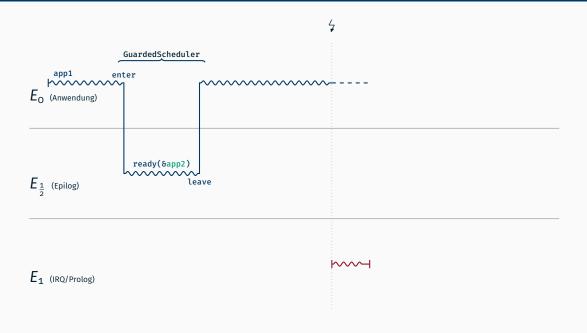

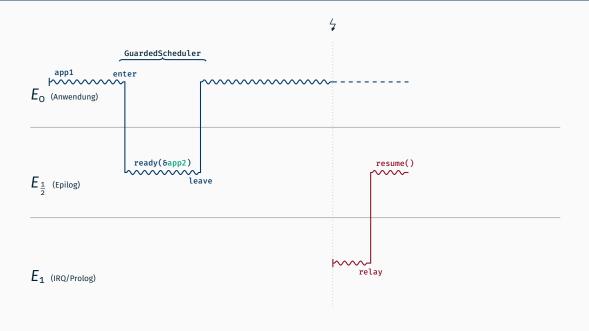

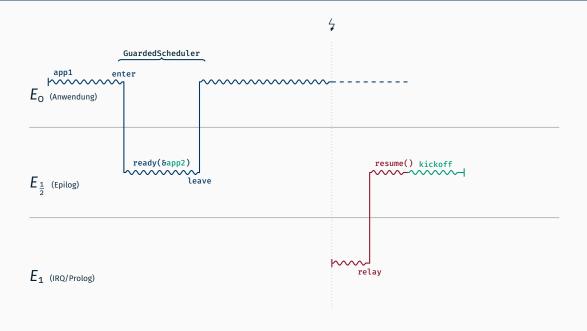

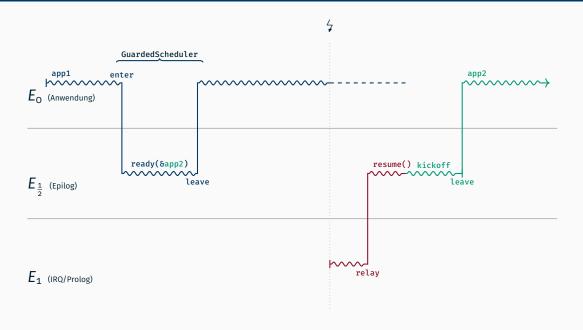

$$E_{\text{O}}^{\text{app1}}$$

(Anwendung)

$$E_{\frac{1}{2}}$$

(Epilog)

$$E_1$$

(IRQ/Prolog)

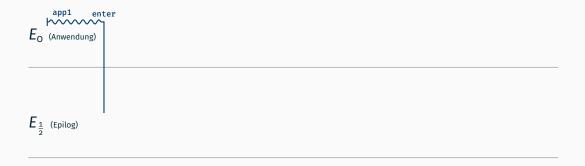

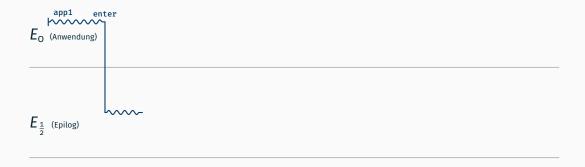

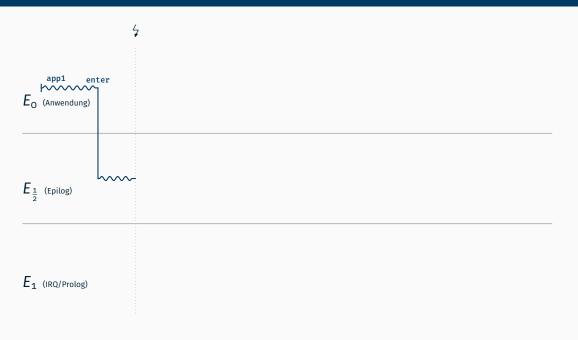

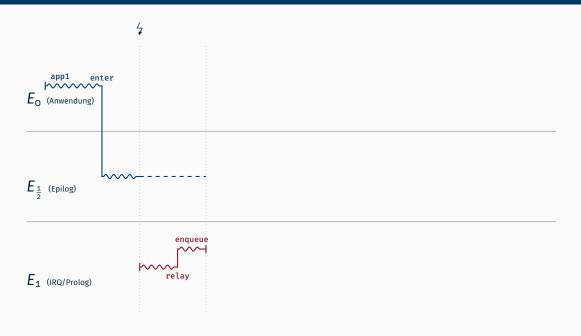

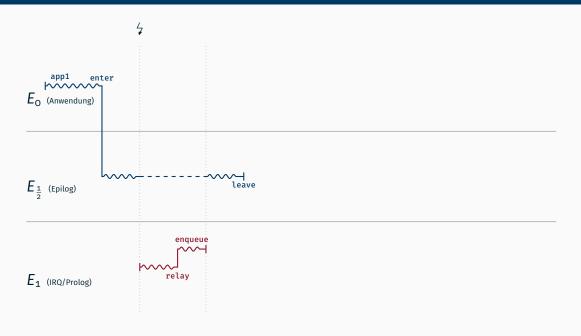

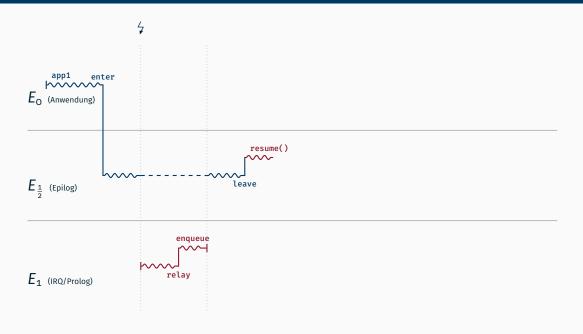

# Ablaufbeispiel bei Faden in Systemebene

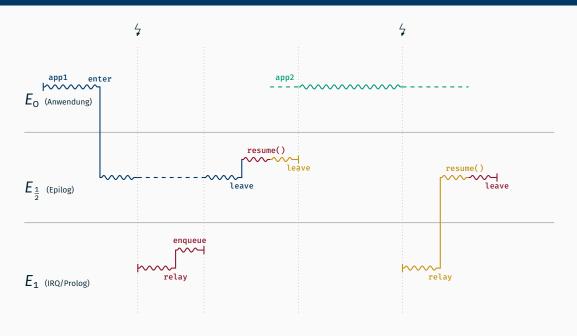

$$E_{\frac{1}{2}}$$

(Epilog)

$$E_1$$

(IRQ/Prolog)

# Ablaufbeispiel bei Faden in Systemebene

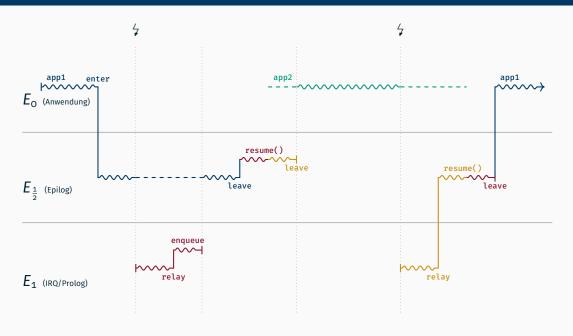

$$E_1$$

(IRQ/Prolog)

$$E_1$$

(IRQ/Prolog)

$$E_{\frac{1}{2}}$$

(Epilog)

$$E_1$$

(IRQ/Prolog)

$$E_1$$

(IRQ/Prolog)

$$E_1$$

(IRQ/Prolog)

$$E_1$$

(IRQ/Prolog)

Besonderheiten

Präemptives Beenden mittels Scheduler::kill(Thread&)

OOStuBS keine Änderung

Präemptives Beenden mittels Scheduler::kill(Thread&)

OOStuBS keine Änderung: aus der Ready-Liste entfernen bzw. Kill-Flag setzen und bei resume prüfen

Präemptives Beenden mittels Scheduler::kill(Thread&)

**OOStuBS** *keine Änderung:* aus der Ready-Liste entfernen bzw. Kill-Flag setzen und bei resume prüfen

**MPStuBS** der Anwendungsfaden kann gerade auf einer anderen CPU laufen

Präemptives Beenden mittels Scheduler::kill(Thread&)

**OOStuBS** *keine Änderung:* aus der Ready-Liste entfernen bzw. Kill-Flag setzen und bei resume prüfen

**MPStuBS** der Anwendungsfaden kann gerade auf einer anderen CPU laufen

Kill-Flag setzen (wie gehabt)

- OOStuBS keine Änderung: aus der Ready-Liste entfernen bzw. Kill-Flag setzen und bei resume prüfen

- **MPStuBS** der Anwendungsfaden kann gerade auf einer anderen CPU laufen

- Kill-Flag setzen (wie gehabt)

- falls er nicht in der Ready-Liste ist, läuft er wohl gerade auf einer anderen CPU

- OOStuBS keine Änderung: aus der Ready-Liste entfernen bzw. Kill-Flag setzen und bei resume prüfen

- **MPStuBS** der Anwendungsfaden kann gerade auf einer anderen CPU laufen

- Kill-Flag setzen (wie gehabt)

- falls er nicht in der Ready-Liste ist, läuft er wohl gerade auf einer anderen CPU

- diese andere CPU muss benachrichtigt werden

- OOStuBS keine Änderung: aus der Ready-Liste entfernen bzw. Kill-Flag setzen und bei resume prüfen

- **MPStuBS** der Anwendungsfaden kann gerade auf einer anderen CPU laufen

- Kill-Flag setzen (wie gehabt)

- falls er nicht in der Ready-Liste ist, läuft er wohl gerade auf einer anderen CPU

- diese andere CPU muss benachrichtigt werden

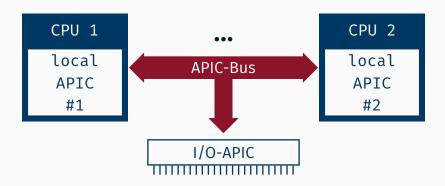

- → INTER PROCESSOR INTERRUPT (IPI)

- OOStuBS keine Änderung: aus der Ready-Liste entfernen bzw. Kill-Flag setzen und bei resume prüfen

- **MPStuBS** der Anwendungsfaden kann gerade auf einer anderen CPU laufen

- Kill-Flag setzen (wie gehabt)

- falls er nicht in der Ready-Liste ist, läuft er wohl gerade auf einer anderen CPU

- diese andere CPU muss benachrichtigt werden

- → INTER PROCESSOR INTERRUPT (IPI)

- die angesprochene CPU muss dann das Kill-Flag des aktuellen Prozesses prüfen

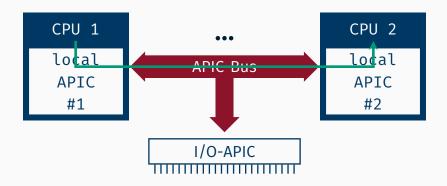

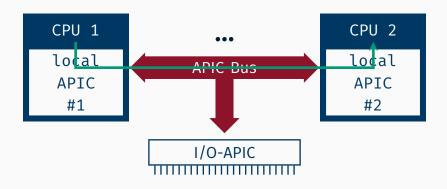

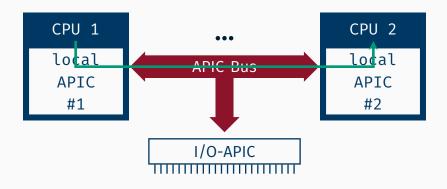

#### **Inter Processor Interrupt**

#### **Inter Processor Interrupt**

#### **Inter Processor Interrupt**

LAPIC::IPI::send(destination, vector);

## **Inter Processor Interrupt**

```

LAPIC::IPI::send(destination, vector);

Interrupt

```

## **Inter Processor Interrupt**

## **Inter Processor Interrupt**

Was kann hier schon schief gehen?

```

lock[Core::getID()] = true;

```

## Was kann hier schon schief gehen?

```

lock[Core::getID()] = true;

```

#### Viel - diese Zeile wird nicht atomar ausgeführt:

```

; Array lock an Adresse 0x2000

call <Core::getID()>

mov [rax+0x2000], 0x1

```

#### Was kann hier schon schief gehen?

```

lock[Core::getID()] = true;

```

#### Viel - diese Zeile wird nicht atomar ausgeführt:

```

; Array lock an Adresse 0x2000

call <Core::getID()>

mov [rax+0x2000], 0x1

4 Scheduler Interrupt

```

Was passiert nun, wenn der Anwendungsfaden anschließend auf einer anderen CPU eingeplant wird?

Kann nun eine fehlerhafte Anwendung unser Betriebssystem blockieren?

- Kann nun eine fehlerhafte Anwendung unser Betriebssystem blockieren?

- Ist unser implementiertes Schedulingverfahren fair?

- Kann nun eine fehlerhafte Anwendung unser Betriebssystem blockieren?

- Ist unser implementiertes Schedulingverfahren fair?

- Unter welchen Umständen wäre es effizienter, den Timer abzuschalten (Stichwort tickless)?

- Kann nun eine fehlerhafte Anwendung unser Betriebssystem blockieren?

- Ist unser implementiertes Schedulingverfahren fair?

- Unter welchen Umständen wäre es effizienter, den Timer abzuschalten (Stichwort tickless)?

- Sollen wir beim IPI in Scheduler::kill auf Antwort warten?

# Fragen?