# Betriebssystemtechnik

Adressräume: Trennung, Zugriff, Schutz

I. Einleitung

Wolfgang Schröder-Preikschat / Volkmar Sieh

19. April 2023

# Gliederung

Einführung Motivation Grundlagen Inhalt

Organisation

Voraussetzungen Veranstaltungsbetrieb Leistungsnachweise

Anhang

$\sim$  in räumlicher Hinsicht  $\sim$  BST

- ~ in räumlicher Hinsicht → BST

- Angriffssicherheit (security)

- Schutz einer Entität vor seiner Umgebung

- Immunität

- verhindern, in einen Adressraum einbrechen zu können

- ~ in räumlicher Hinsicht → BST

- Angriffssicherheit (security)

- Schutz einer Entität vor seiner Umgebung

- Immunität

- verhindern, in einen Adressraum einbrechen zu können

- Betriebssicherheit (safety)

- Schutz der Umgebung vor einer Entität

- Isolation

- verhindern, aus einem Adressraum ausbrechen zu können

- ~ in zeitlicher Hinsicht → EZS[3]

- Einhaltung von Terminen, Vermeidung von Interferenzen

~ in energetischer Hinsicht

Abfederung von Energiespitzen, Einhaltung von Energiebudgets

- ~ in räumlicher Hinsicht → BST

- Angriffssicherheit (security)

- Schutz einer Entität vor seiner Umgebung

- Immunität

- verhindern, in einen Adressraum einbrechen zu können

- Betriebssicherheit (safety)

- Schutz der Umgebung vor einer Entität

- Isolation

- verhindern, aus einem Adressraum ausbrechen zu können

## JITTY

- Linux-binär-kompatibler Betriebssystemkern

- programmiert von Mitarbeitern und Studentinnen und Studenten

- ,sauberer" Source-Code

- nur ca. 150k LOC (inkl. vielen Kommentaren)

- Code f

ür Lehrstuhlprojekte

- Beispiel-Code für BS und BST

- https://gitlab.cs.fau.de/i4/jitty/jitty-os.git

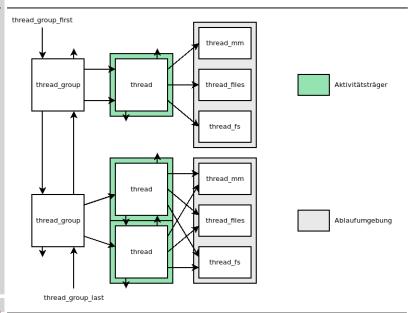

#### **Prozess**

### Definitionen:

## Ablaufumgebung (Task):

Menge von Code, Daten, offene Dateien, usw.

### Aktivitätsträger (Thread):

Einheit, die Code ausführen kann

### typischer Unix Prozess:

eine Ablaufumgebung mit einem Aktivitätsträger

### hier: Prozess:

eine Ablaufumgebung mit ggf. mehreren Aktivitätsträgern

## Prozess - Beispiel JITTY

## Feingranulare Unterteilung der Ablaufumgebung:

```

struct thread {

2

struct thread *prev:

3

struct thread *next;

struct thread_mm {

4

5

struct thread mm *mm:

struct mm reg *reg first:

6

struct thread files *files:

struct mm reg *reg last:

7

struct thread_fs *fs;

1:

8

9

long reg[8]:

struct thread files {

10

uint8_t stack[16*1024];

11

}:

struct file *file[256]:

12

10

}:

13

struct thread_group {

11

14

struct thread group *prev;

12

struct thread_fs {

15

struct thread group *next:

13

16

14

struct dentry *root;

17

struct thread_group *parent;

15

struct dentry *cwd;

struct thread group *child first:

18

16

}:

struct thread group *child next:

17

19

20

18

struct thread_group *thread_group_first;

21

19

struct thread group *thread group last:

struct thread *first:

22

struct thread *last:

23

};

```

# Prozess - Beispiel JITTY

- realer ~

- reflektiert die phys(ikal)ischen Eigenschaften des Rechensystems

- nicht zu jeder Adresse gibt es einen Adressaten (Speicher, Geräte)

- die Bindung zwischen beiden ist fest, zur Laufzeit unveränderlich

- Vorsicht: Speicherbankumschaltung oder PCI-Config-Space

- realer ~

- reflektiert die phys(ikal)ischen Eigenschaften des Rechensystems

- nicht zu jeder Adresse gibt es einen Adressaten (Speicher, Geräte)

- die Bindung zwischen beiden ist fest, zur Laufzeit unveränderlich

- Vorsicht: Speicherbankumschaltung oder PCI-Config-Space

- ungültige Adressen implizieren undefiniertes/fehlerhaftes Verhalten

- Vorsicht: Probing von Geräten beim Booten

- logischer ~

- reflektiert die strukturellen Eigenschaften eines Programms

- zu jeder Adresse gibt es immer einen (speicher-) residenten Adressaten

- die Bindung zwischen beiden ist jedoch lose, zur Laufzeit veränderlich

- Beispiele: brk, sbrk, mmap, munmap, malloc/free, Stack

#### ■ logischer ~

- reflektiert die strukturellen Eigenschaften eines Programms

- zu jeder Adresse gibt es immer einen (speicher-) residenten Adressaten

- die Bindung zwischen beiden ist jedoch lose, zur Laufzeit veränderlich

- Beispiele: brk, sbrk, mmap, munmap, malloc/free, Stack

- ungültige Adressen innerhalb des Adressraums gibt es nicht

- Vorsicht: Unterschied zwischen Segmentierung und Seitennummerierung

- virtueller ~

- reflektiert die gegenwärtige/zukünftige Auslastung des Rechensystems

- zu einer Adresse kann es zeitweilig einen nichtresidenten Adressaten geben

- virtueller ~

- reflektiert die gegenwärtige/zukünftige Auslastung des Rechensystems

- zu einer Adresse kann es zeitweilig einen nichtresidenten Adressaten geben

ansonsten "erben" die Adressen alle Eigenschaften logischer Adressräume

Adressraum (vgl. auch [4])

■ realer ~

reflektiert die phys(ikal)ischen Eigenschaften des Rechensystems

■ logischer ~

reflektiert die strukturellen Eigenschaften eines Programms

ı virtueller ∼

• reflektiert die gegenwärtige/zukünftige Auslastung des Rechensystems

### Adressen

### Beispiel Intel:

Segment-Nummer und Offset

lineare Adresse

٧

physikalische Adresse

virtuelle Adresse?

### realer Adressraum

### Beispiel IBM-AT:

```

DRAM

0x000000000

0x0009ffff

reserviert für VGA-Grafik

0x000a0000

0x000b7fff

0x000b8000

0x000bffff

VGA-Text

VGA-BIOS

0x000c0000

0 \times 0 0 0 c f f f f

reserviert für z.B. BIOS-Ext

0000b000x0

0x000dffff

0x000e0000

0x000fffff

BIOS

0 \times 00100000

0x00efffff

DRAM

0x00f00000

0x00ffffff

reserviert für ISA-I/O

DRAM

0 \times 01000000

BIOS

0xfffe0000

0xffffffff

```

Was passiert bei Zugriff auf nicht zugewiesene Speicherbereiche?

Segmentierung oder Eingrenzung von Programmen

### Segmentierung oder Eingrenzung von Programmen:

- $\blacksquare$  Maschinenprogrammebene (Ebene 3)

- der Prozessor ermöglicht Immunität/Isolation in Hardware

- MMU (Abk. memory management unit) . . . . . logischer Adressraum

- MPU (Abk. memory protection unit) . . . . . . . . phys(ikal)ischer Adressraum

- das Betriebssystem programmiert diese Hardware problemspezifisch

Segmentierung oder Eingrenzung von Programmen:

- $\blacksquare$  Programmiersprachenebene (Ebene  $_5$ )

- der Compiler ermöglicht Immunität/Isolation in Software

- Programme liegen in einer typsicheren Programmiersprache vor

Segmentierung oder Eingrenzung von Programmen:

■ Maschinenprogrammebene (Ebene 3)

Programmiersprachenebene (Ebene 5)

Prozesse können die durch ihren logischen Adressraum jew. definierte Schutzdomäne nicht oder nur kontrolliert verlassen

Segmentierung oder Eingrenzung von Programmen:

■ Maschinenprogrammebene (Ebene 3)

Programmiersprachenebene (Ebene 5)

Prozesse können die durch ihren logischen Adressraum jew. definierte Schutzdomäne nicht oder nur kontrolliert verlassen

- Abwesenheit von Prozessor- und Speicherfehlern vorausgesetzt

- je nach Abstraktionsebene aber mit unterschiedlichem Wirkungsfeld

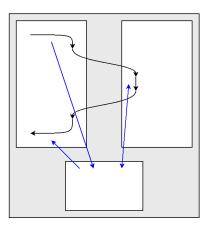

- durch Wechsel der Schutzdomäne

- prozedurbasierte Technik

- Systemaufruf, leichtgewichtiger Fernaufruf

- Kontrollflussfortsetzung im anderen Adressraum

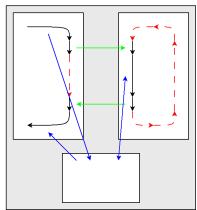

- koroutinenbasierte Technik

- Nachrichtenversenden, Fernaufruf

- Kontrollflusswechsel hin zum anderen Adressraum

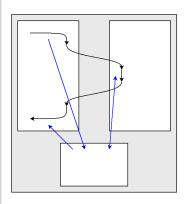

- durch Mitbenutzung (sharing) von Adressraumbereichen

- Datenverbund (data sharing)

- mit gleichförmigen oder ungleichförmigen Lese-/Schreibrechten

- Gemeinschaftsbibliothek (shared library)

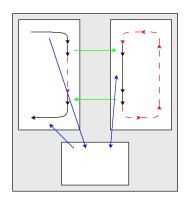

Grenzen überschreitende Operationen als Folge der Trennung

durch Wechsel der Schutzdomäne

durch Mitbenutzung (sharing) von Adressraumbereichen

- durch Kombinierung beider Ansätze

- Einrichtung eines Datenverbunds beim Wechsel der Schutzdomäne

- aus dem "eingewechselten Adressraum" heraus veranlasst

- zum Lesen/Schreiben von Entitäten des "ausgewechselten Adressraums"

## Grenzen überschreitende Operationen als Folge der Trennung

#### Vorteile:

- keine unnötigen Threads/Kontextwechsel Nachteile:

- ggf. Verlust von Cache-Inhalten

- Kontextwechsel über BS

Grenzen überschreitende Operationen als Folge der Trennung

#### Vorteile:

- Cache-Inhalte bleiben erhalten

Nachteile:

- mehr Threads/Kontextwechsel

- send/recv über BS

- hardwarebasiert, segment- oder seitenoriertiert

- MMU/MPU vergleicht Zugriffsart und Zugriffsrecht

- Lesen, Schreiben, Ausführen auch in Kombination

- CPU begeht Ausnahme von normaler Programmausführung

- lässt den aktuellen Maschinenbefehl in die Falle (trap, exception) laufen

- bewirkt damit eine synchrone Programmunterbrechung

- Betriebssystem führt Ausnahmebehandlung [2] durch

- Wiederaufnahmemodell: Fortsetzung des unterbrochenen Prozesses

- Beendigungsmodell: Abbruch des unterbrochenen Prozesses

- softwarebasiert, datentyporientiert ⇒ sprachbasiert

- Laufzeitsystem d. h., der Prozess selbst führt o. g. Funktionen durch

- bestimmte Überprüfungen nimmt jedoch bereits der (JIT-) Compiler vor

- alle statisch, also vor Laufzeit, entscheidbaren Zugriffsoperationen

hardwarebasiert, segment- oder seitenoriertiert

■ softwarebasiert, datentyporientiert ⇒ sprachbasiert

- in Synergie beider Ansätze: Befähigung (capability, [1])

- befähigungsbasierte Systeme sind kompliziert obwohl ideal zum Schutz

#### Vorlesung

- Wissen zu Adressraumkonzepten von Betriebssystemen vertiefen

- Verstehen über (logische) Adressräume festigen

- inhaltliches Begreifen verschiedener Facetten von Adressräumen

- intellektuelle Erfassung des Zusammenhangs, in dem Adressräume stehen

#### Vorlesung

- Wissen zu Adressraumkonzepten von Betriebssystemen vertiefen

- Verstehen über (logische) Adressräume festigen

- inhaltliches Begreifen verschiedener Facetten von Adressräumen

- intellektuelle Erfassung des Zusammenhangs, in dem Adressräume stehen

- Anwenden ausgewählter Vorlesungsinhalte für StuBS

- Analyse der Anforderungen an und Gegebenheiten von StuBS

- Synthese von Adressraumabstraktionen und StuBS

- Evaluation des erweiterten StuBS<sub>ml</sub>: Vorher-nachher-Vergleicl

#### Vorlesung

- Wissen zu Adressraumkonzepten von Betriebssystemen vertiefen

- Verstehen über (logische) Adressräume festigen

- inhaltliches Begreifen verschiedener Facetten von Adressräumen

- intellektuelle Erfassung des Zusammenhangs, in dem Adressräume stehen

- Anwenden ausgewählter Vorlesungsinhalte für StuBS

- Analyse der Anforderungen an und Gegebenheiten von StuBS

- Synthese von Adressraumabstraktionen und StuBS

- Evaluation des erweiterten StuBS<sub>ml</sub>: Vorher-nachher-Vergleich

#### Vorlesung

- Wissen zu Adressraumkonzepten von Betriebssystemen vertiefen

- Verstehen über (logische) Adressräume festigen

- inhaltliches Begreifen verschiedener Facetten von Adressräumen

- intellektuelle Erfassung des Zusammenhangs, in dem Adressräume stehen

- Anwenden ausgewählter Vorlesungsinhalte für StuBS

- Analyse der Anforderungen an und Gegebenheiten von StuBS

- Synthese von Adressraumabstraktionen und StuBS

- *Evaluation* des erweiterten StuBS<sub>m/</sub>: Vorher-nachher-Vergleich

#### Vorlesung

- Wissen zu Adressraumkonzepten von Betriebssystemen vertiefen

- Verstehen über (logische) Adressräume festigen

- inhaltliches Begreifen verschiedener Facetten von Adressräumen

- intellektuelle Erfassung des Zusammenhangs, in dem Adressräume stehen

- Anwenden ausgewählter Vorlesungsinhalte für StuBS

- Analyse der Anforderungen an und Gegebenheiten von StuBS

- Synthese von Adressraumabstraktionen und StuBS

- Evaluation des erweiterten StuBS<sub>ml</sub>: Vorher-nachher-Vergleich

#### Einflussfaktoren

- Systemaufrufe: Befehlsformate der Machinenprogrammebene

- Betriehssystemarchitektur: {Nano Mikro Makro Exo}kern

- The the California In the Davidson American

- Adressraumkonzepte

- Seitenadressierung: ein-/mehrstufig, invertiert, spärlich

- Segmentadressierung: pur, seitenbasierte Hybride

JV v

ÜV

#### Einflussfaktoren

- Systemaufrufe: Befehlsformate der Machinenprogrammebene

- Betriebssystemarchitektur: {Nano,Mikro,Makro,Exo}kern

- Hierarchien: Schichtenstruktur von Betriebssystemen

- Adressraumkonzepte

- Seitenadressierung: ein-/mehrstufig, invertiert, spärlich

- Segmentadressierung: pur, seitenbasierte Hybride

ÜV

ÜV

- Einflussfaktoren

- Systemaufrufe: Befehlsformate der Machinenprogrammebene

- Betriebssystemarchitektur: {Nano,Mikro,Makro,Exo}kern

- Hierarchien: Schichtenstruktur von Betriebssystemen

- - Seitenadressierung: ein-/mehrstufig, invertiert, spärlich

- Segmentadressierung: pur. seitenbasierte Hybride

ÜV

- Einflussfaktoren

- Systemaufrufe: Befehlsformate der Machinenprogrammebene

- Betriebssystemarchitektur: {Nano,Mikro,Makro,Exo}kern

- Hierarchien: Schichtenstruktur von Betriebssystemen

UV

**v**

- Adressraumkonzente

- Seitenadressierung: ein-/mehrstufig, invertiert, spärlich

- Segmentadressierung: pur, seitenbasierte Hybride

ÜV

V

ÜV

- Einflussfaktoren

- Systemaufrufe: Befehlsformate der Machinenprogrammebene

- Betriebssystemarchitektur: {Nano,Mikro,Makro,Exo}kern

- Hierarchien: Schichtenstruktur von Betriebssystemen

V

V

- Adressraumkonzepte

- Seitenadressierung: ein-/mehrstufig, invertiert, spärlich

- Segmentadressierung: pur, seitenbasierte Hybride

U V

ÜV

- Einflussfaktoren

- Systemaufrufe: Befehlsformate der Machinenprogrammebene

- Betriebssystemarchitektur: {Nano,Mikro,Makro,Exo}kern

- Hierarchien: Schichtenstruktur von Betriebssystemen

V

- Adressraumkonzepte

- Seitenadressierung: ein-/mehrstufig, invertiert, spärlich

- Segmentadressierung: pur, seitenbasierte Hybride

ÜV

ÜV

- Einflussfaktoren

- Systemaufrufe: Befehlsformate der Machinenprogrammebene

- Betriebssystemarchitektur: {Nano,Mikro,Makro,Exo}kern

- Hierarchien: Schichtenstruktur von Betriebssystemen

V

- Adressraumkonzepte

- Seitenadressierung: ein-/mehrstufig, invertiert, spärlich

- Segmentadressierung: pur, seitenbasierte Hybride

ÜV

ÜV

- Einflussfaktoren

- Systemaufrufe: Befehlsformate der Machinenprogrammebene

- Betriebssystemarchitektur: {Nano,Mikro,Makro,Exo}kern

- Hierarchien: Schichtenstruktur von Betriebssystemen

- Adressraumkonzepte

- Seitenadressierung: ein-/mehrstufig, invertiert, spärlich

- Segmentadressierung: pur, seitenbasierte Hybride

ς

Adressraummodelle

- Mehradressraumsystem: total/partiell privat

- Einadressraumsystem: Randomisierung, Befähigungen

ÜV

Spezialfälle

- adaptiver Hauptspeicherschutz: TLB, typsichere Programme

- virtuell gemeinsamer Speicher: seitenbasierte "IPC

- virtuell nicht-flüchtiger Hauptspeicher: NVRAM, Transparenz

- dynamisches Binden: Gemeinschaftsbibliotheken

V

Nachlese, Ausblick

\ /

S

- Adressraummodelle

- Mehradressraumsystem: total/partiell privat

UV

- Einadressraumsystem: Randomisierung, Befähigungen

- Spezialfälle

- adaptiver Hauptspeicherschutz: TLB, typsichere Programme

- virtuell gemeinsamer Speicher: seitenbasierte "IPC"

- virtuell nicht-flüchtiger Hauptspeicher: NVRAM, Transparenz

- dynamisches Binden: Gemeinschaftsbibliotheken

- Nachlese, Ausblick

V

9

- Adressraummodelle

- Mehradressraumsystem: total/partiell privat

ÜV

- Einadressraumsystem: Randomisierung, Befähigungen

- Spezialfälle

- adaptiver Hauptspeicherschutz: TLB, typsichere Programme

- Virtuen gemeinsamer Speicher, Seitembasierte "IFC

- virtuell nicht-flüchtiger Hauptspeicher: NVRAM, Transparenz

- dynamisches Binden: Gemeinschaftsbibliotheken

- Nachlese, Ausblick

v

- Adressraummodelle

- Mehradressraumsystem: total/partiell privat

- Einadressraumsystem: Randomisierung, Befähigungen

UV V

- Spezialfälle

- adaptiver Hauptspeicherschutz: TLB, typsichere Programme

virtuell gemeinsamer Speicher: seitenbasierte IPC"

- virtuell nicht-flüchtiger Hauptspeicher: NVRAM, Transparenz

- dynamisches Binden: Gemeinschaftsbibliotheken

V

Nachlese, Ausblick

\/

- -

- Adressraummodelle

- Mehradressraumsystem: total/partiell privat

- Einadressraumsystem: Randomisierung, Befähigungen

V

### Spezialfälle

- adaptiver Hauptspeicherschutz: TLB, typsichere Programme

- virtuell gemeinsamer Speicher: seitenbasierte "IPC"

- virtuell nicht-flüchtiger Hauptspeicher: NVRAM, Transparenz

- dynamisches Binden: Gemeinschaftsbibliotheken

v

Nachlese, Ausblick

\/

- Sprachbasierung: Systemprogrammiersprachen

- 1

- Adressraummodelle

- Mehradressraumsystem: total/partiell privat

- Einadressraumsystem: Randomisierung, Befähigungen

- Spezialfälle

- adaptiver Hauptspeicherschutz: TLB, typsichere Programme

- virtuell gemeinsamer Speicher: seitenbasierte "IPC"

- virtuell nicht-flüchtiger Hauptspeicher: NVRAM, Transparenz

- dynamisches Binden: Gemeinschaftsbibliotheken

... jeweils mit Beispielen aus der Praxis.

1) ——

- Sprachbasierung: Systemprogrammiersprachen

- Adressraummodelle

- Mehradressraumsystem: total/partiell privatEinadressraumsystem: Randomisierung, Befähigungen

- en V

- Spezialfälle

- adaptiver Hauptspeicherschutz: TLB, typsichere Programme

- virtuell gemeinsamer Speicher: seitenbasierte "IPC"

- virtuell nicht-flüchtiger Hauptspeicher: NVRAM, Transparenz

- dynamisches Binden: Gemeinschaftsbibliotheken

- Nachlese, Ausblick

$\vee$

3

- Adressraummodelle

- Mehradressraumsystem: total/partiell privat

UV

- Einadressraumsystem: Randomisierung, Befähigungen

- Spezialfälle

- adaptiver Hauptspeicherschutz: TLB, typsichere Programme

- virtuell gemeinsamer Speicher: seitenbasierte "IPC"

- virtuell nicht-flüchtiger Hauptspeicher: NVRAM, Transparenz

- dynamisches Binden: Gemeinschaftsbiblioth

V

Machiese, Ausbrick

- Adressraummodelle

- Mehradressraumsystem: total/partiell privatEinadressraumsystem: Randomisierung, Befähigungen

V V

- Spezialfälle

- adaptiver Hauptspeicherschutz: TLB, typsichere Programme

- virtuell gemeinsamer Speicher: seitenbasierte "IPC"

- virtuell nicht-flüchtiger Hauptspeicher: NVRAM, Transparenz

- dynamisches Binden: Gemeinschaftsbibliotheken

Nachlese, Ausblick

ÜV V

3

- Adressraummodelle

- Mehradressraumsystem: total/partiell privatEinadressraumsystem: Randomisierung, Befähigungen

UV

- Spezialfälle

- adaptiver Hauptspeicherschutz: TLB, typsichere Programme

- virtuell gemeinsamer Speicher: seitenbasierte "IPC"

- virtuell nicht-flüchtiger Hauptspeicher: NVRAM, Transparenz

dynamisches Binden: Gemeinschaftsbibliotheken

Nachlese, Ausblick

ÜV

ia...aila mait Daiamialam acca dan Duaccia

# Gliederung

Einführung Motivation Grundlagen

### Organisation

Voraussetzungen Veranstaltungsbetrieb Leistungsnachweise

Anhang

Voraussetzung

### Softwaresysteme

- SP, SPiC

- BS ⇔ StuBS

# Programmiersysteme

- C, C++, make

- ASM

# Hardwaresysteme

- ×86/×86\_64

- Mehrkerner

# Voraussetzung

# Softwaresysteme

- SP, SPiC

- BS ⇔ StuBS

# Programmiersysteme

- C, C++, make

- ASM

### Hardwaresysteme

- x86/x86\_64

- Mehrkerner

## Erfahrung

- in der hardwarenahen Programmierung

- Gerätetreiber, Unterbrechungsbehandlung, Prozesswechsel

- in der Fehlersuche/-beseitigung (debugging) in Betriebssystemen

- nichtsequentielle Programme, mehrkernige Prozessoren

- in der projektorientierten Entwicklung nativer Systemprogramme

# Voraussetzung

# Softwaresysteme

- SP, SPiC

- BS ⇔ StuBS

# Programmiersysteme

- C, C++, make

- ASM

### Hardwaresysteme

- x86/x86\_64

- Mehrkerner

# Erfahrung

- in der hardwarenahen Programmierung

- Gerätetreiber, Unterbrechungsbehandlung, Prozesswechsel

- in der Fehlersuche/-beseitigung (debugging) in Betriebssystemen

- nichtsequentielle Programme, mehrkernige Prozessoren

- in der projektorientierten Entwicklung nativer Systemprogramme

#### Erwartung

intrinsische Motivation, kritisches Denken, positive Fehlerkultur

### Unterrichtstermine

- Vorlesungs-, Übungs- und Rechnerzeiten:

- auf sys.cs.fau.de dem Reiter "Lehre" folgen

# Unterrichtstermine und -sprache

- Vorlesungs-, Übungs- und Rechnerzeiten:

- auf sys.cs.fau.de dem Reiter "Lehre" folgen

- Unterrichtssprache:

Vorlesung und Übung

# Unterrichtstermine und -sprache

- Vorlesungs-, Übungs- und Rechnerzeiten:

- auf sys.cs.fau.de dem Reiter "Lehre" folgen

- Unterrichtssprache:

■ Vorlesung und Übung

Fachbegriffe

# Unterrichtstermine und -sprache

- Vorlesungs-, Übungs- und Rechnerzeiten:

- auf sys.cs.fau.de dem Reiter "Lehre" folgen

- Unterrichtssprache:

Vorlesung und Übung

Fachbegriffe

- informatische Fachsprache

- Sachwortverzeichnis (in Arbeit und Überarbeitung)

- https://www4.cs.fau.de/DE/~wosch/glossar.pdf

# Übungsbetrieb

- Tafelübung ~> "learning by exploring"

- Anmeldung über WAFFEL¹ (URL siehe Leitseite von BST)

- Übungsaufgaben sind (bevorzugt) in Gruppen zu bearbeiten

<sup>&</sup>lt;sup>1</sup>Abk. für Webanmeldefrickelformular Enterprise Logic

# Übungsbetrieb

- Tafelübung ~> "learning by exploring"

- Anmeldung über WAFFEL¹ (URL siehe Leitseite von BST)

- Übungsaufgaben sind (bevorzugt) in Gruppen zu bearbeiten

- Rechnerarbeit ~> "learning by doing", kein Tafelersatz

- Anmeldung ist nicht vorgesehen, reservierte Arbeitsplätze s.o.

- bei Fragen zu den Übungsaufgaben, Übungsleiter konsultieren

- Email senden bzw. einfach vorbeischauen...

<sup>&</sup>lt;sup>1</sup>Abk. für Webanmeldefrickelformular Enterprise Logic

# Übungsbetrieb

- Tafelübung  $\sim$  "learning by exploring"

- Anmeldung über WAFFEL¹ (URL siehe Leitseite von BST)

- Übungsaufgaben sind (bevorzugt) in Gruppen zu bearbeiten

- Rechnerarbeit → "learning by doing", kein Tafelersatz

- Anmeldung ist nicht vorgesehen, reservierte Arbeitsplätze s.o.

- bei Fragen zu den Übungsaufgaben, Übungsleiter konsultieren

- Email senden bzw. einfach vorbeischauen...

Der. die. das. Wer. wie. was? Wieso, weshalb, warum? Wer nicht fragt, bleibt dumm!

<sup>1</sup>Abk. für Webanmeldefrickelformular Enterprise Logic

### 5 ECTS

- BST und OOStuBS<sub>ml</sub>

- 4 SWS (2 V + 2 Ü)

### 5 ECTS

- BST und OOStuBS<sub>ml</sub>

- 4 SWS (2 V + 2 Ü)

- Prüfungsgespräch

- 30 Minuten

- Stoff zu V + Ü

# 7,5 ECTS

- BST und MPStuBS<sub>ml</sub>

- 6 SWS (2 V + 2 Ü + 2 EÜ)

- erweiterte Übung

- ggf. auch Extraaufgabe

# 7,5 ECTS

- BST und MPStuBS<sub>ml</sub>

- 6 SWS (2 V + 2 Ü + 2 EÜ)

- erweiterte Übung

- ggf. auch Extraaufgabe

- Prüfungsgespräch

- 30 Minuten

- Stoff zu  $V + \ddot{U} + E\ddot{U}$

#### 5 ECTS

- BST und OOStuBS<sub>ml</sub>

- 4 SWS (2 V + 2 Ü)

## 7,5 ECTS

- BST und MPStuBS<sub>ml</sub>

- 6 SWS (2 V + 2 Ü + 2 EÜ)

- erweiterte Übung

- ggf. auch Extraaufgabe

- Prüfungsgespräch

- 30 Minuten

- Stoff zu V + Ü

- Prüfungsgespräch

- 30 Minuten

- Stoff zu V + Ü + EÜ

- erfolgreiche Bearbeitung der Übungsaufgaben ist Voraussetzung

### 5 ECTS

- BST und OOStuBS<sub>ml</sub>

- 4 SWS (2 V + 2 Ü)

## 7.5 ECTS

- BST und MPStuBS<sub>ml</sub>

- 6 SWS (2 V + 2 Ü + 2 EÜ)

- erweiterte Übung

- ggf. auch Extraaufgabe

- Prüfungsgespräch

- 30 Minuten

- Stoff zu V + Ü

- Prüfungsgespräch

- 30 Minuten

- Stoff zu V + Ü + EÜ

- erfolgreiche Bearbeitung der Übungsaufgaben ist Voraussetzung

- Anmeldung zum Prüfungsgespräch per E-Mail an:

- sieh@cs.fau.de = angeben ob 5 oder 7,5 ECTS

- Termin oder Terminfenster mitsenden

- Prüfungszeitraum (Ausnahmen bestätigen die Regel)

# Gliederung

#### Einführung

Motivation

Grundlagen

Inhalt

#### Organisation

Voraussetzungen

Veranstaltungsbetrieb

Leistungsnachweise

# Anhang

### **Kontakt**

- Volkmar Sieh, Dr.-Ing.

- Vorlesung

- sys.cs.fau.de/person/sieh

- Wolfgang Schröder-Preikschat, Prof. Dr.-Ing. habil.

- Vorlesung (ggf. Vertretung)

- sys.cs.fau.de/person/wosch

#### Kontakt

- Volkmar Sieh, Dr.-Ing.

- Vorlesung

- sys.cs.fau.de/person/sieh

- Wolfgang Schröder-Preikschat, Prof. Dr.-Ing. habil.

- Vorlesung (ggf. Vertretung)

- sys.cs.fau.de/person/wosch

- Phillip Raffeck, M. Sc.

- Übungen

- sys.cs.fau.de/person/raffeck

- Dustin Nguyen, M. Sc.

- Übungen

- sys.cs.fau.de/person/nguyen

#### Literaturverzeichnis

- DENNIS, J. B.; HORN, E. C. V.: Programming Semantics for Multiprogrammed Computations. In: Communications of the ACM 9 (1966), März, Nr. 3, S. 143–155

- [2] GOODENOUGH. J. B.: Exception Handling: Issues and a Proposed Notation. In: Communications of the ACM 18 (1975), Nr. 12, S. 683-696

- [3] Schröder-Preikschat, W.: Echtzeitsysteme. http://www4.informatik.uni-erlangen.de/Lehre/WS05/V EZS, 2005 ff.

- [4] Schröder-Preikschat, W.: Kleinöder, J.: Systemprogrammierung. http://www4.informatik.uni-erlangen.de/Lehre/WS08/V\_SP, 2008 ff.